## LCD MODULE SPECIFICATION

Model: CG240160D - \_ \_ - \_ - \_ - \_

| Revision      | 00           |

|---------------|--------------|

| Engineering   | Jackson Fung |

| Date          | 19 June 2015 |

| Our Reference | X9058        |

ADDRESS: 1<sup>st</sup> FLOOR, EFFICIENCY HOUSE, 35 TAI YAU STREET, SAN PO KONG,

KOWLOON, HONG KONG.

TEL : (852) 2341 3238 (SALES OFFICE) (852) 2342 8228 (GENERAL OFFICE)

FAX : (852) 2357 4237 (SALES OFFICE)

E-MAIL : <u>cdl@cloverdisplay.com</u>

URL : <a href="http://www.cloverdisplay.com">http://www.cloverdisplay.com</a>

#### **MODE OF DISPLAY**

Display mode **Display condition** Viewing direction STN: Yellow green 6 O' clock Reflective type Grey Transflective type ☐ 12 O' clock Blue (negative) Transmissive type 3 O' clock FSTN positive Others 9 O' clock ☐ FSTN negative LCD MODULE NUMBER NOTATION: CG240160D - N N - S R - N 6 - T \*(1)---Model number of standard LCD Modules \*(2)---Backlight type (1) (2) (3) (4) (5) (6) (7) (8) N – No backlight E – EL backlight L – Side-lited LED backlight M- Array LED backlight C - CCFL\*(3)---Backlight color N – No backlight A - AmberB – Blue O- Orange W-White Y - Yellow green \*(4)---Display mode T - TNV – TN (Negative) S – STN Yellow green G – STN Grey B – STN Blue (Negative) F - FSTNN – FSTN (Negative) \*(5)---Rear polarizer type R – Reflective F – Transflective T – Transmissive \*(6)---Temperature range N - NormalW-Extended \*(7)---Viewing direction 6-6 O'clock 2 – 12 O'clock 3 - 3 O'clock 9 – 9 O'clock \*(8)---Special code for other requirements

SPEC. REV.00 PAGE 1 OF 22

(Can be omitted if not used)

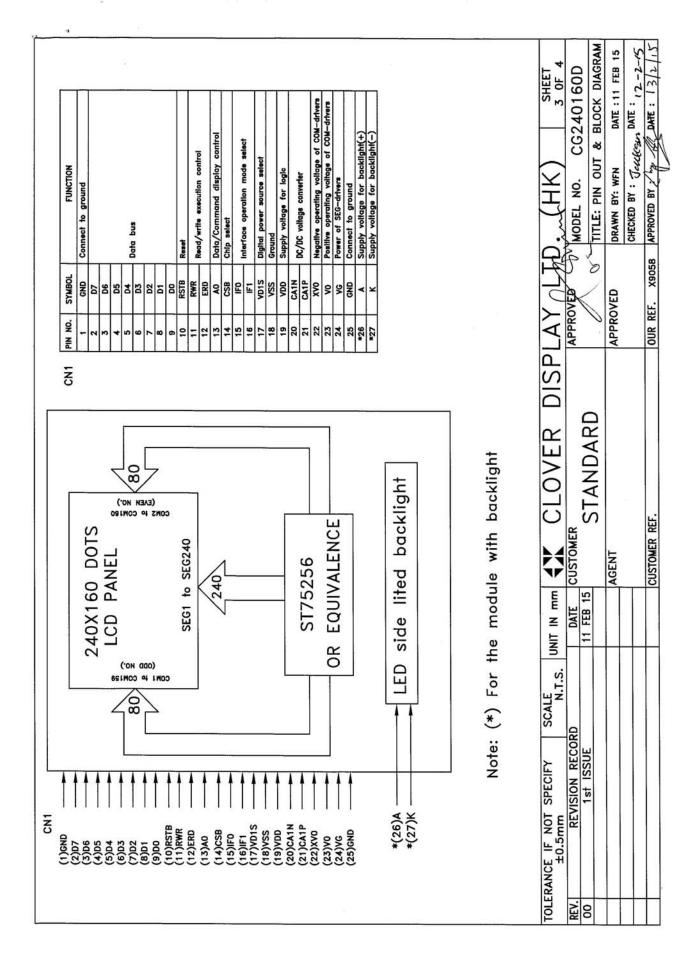

#### **GENERAL DESCRIPTION**

Display mode : 240 X 160 dots graphic COG LCD module

Interface : 8-bit parallel / 4-line serial

Driving method : 1/160 duty, 1/14 bias

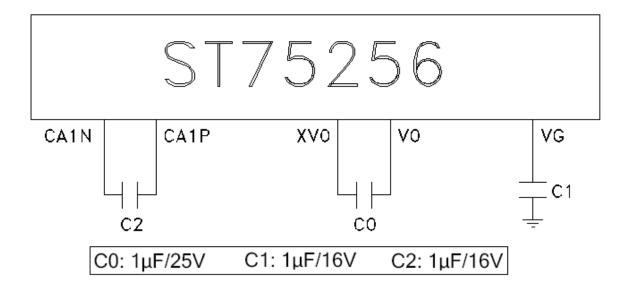

Controller IC : Sitronix ST75256 or equivalent

For the detailed information, please refer to the IC specifications.

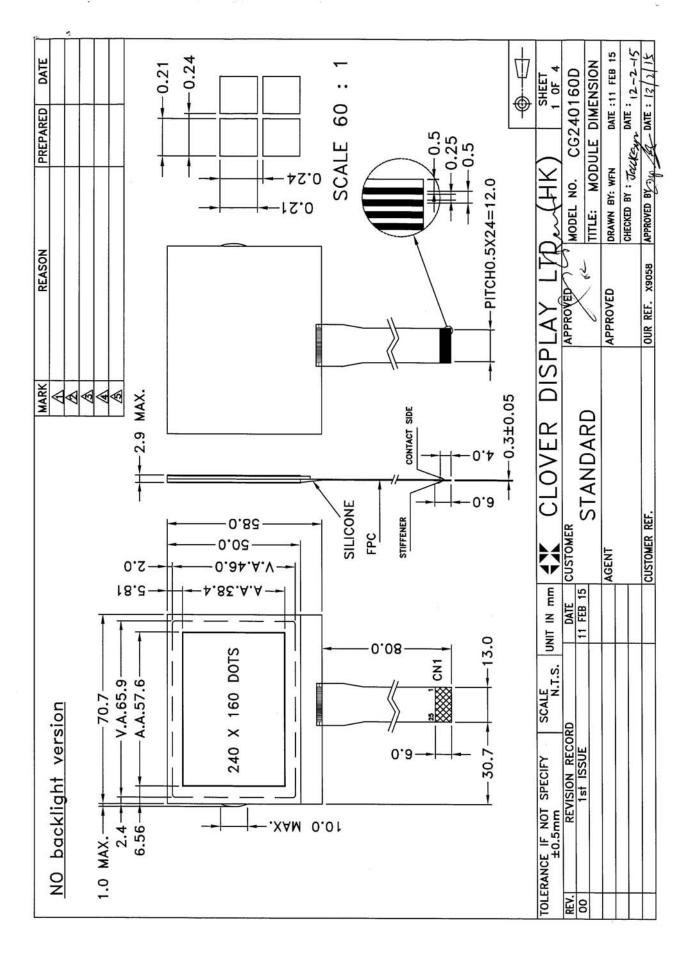

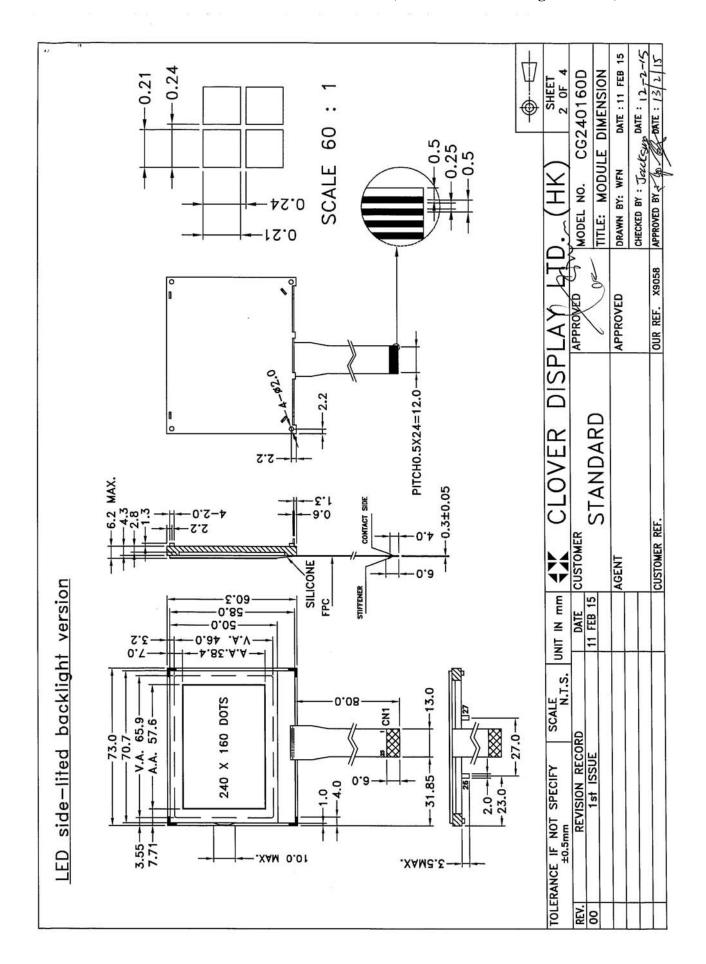

#### **MECHANICAL DIMENSIONS**

| Item                     | Dimension                  | Unit | Item         | Dimension       | Unit |

|--------------------------|----------------------------|------|--------------|-----------------|------|

| Outline Dimension        |                            | mm   | Dot Pitch    | 0.24(L)x0.24(W) | mm   |

| No Backlight             | 70.7(L)x58.0(W)x2.9MAX.(H) | mm   | Dot Size     | 0.21(L)x0.21(W) | mm   |

| LED side-lited backlight | 73.0(L)x60.3(W)x6.2MAX.(H) | mm   | Viewing Area | 65.9(L)x46.0(W) | mm   |

#### **CONNECTOR PIN ASSIGNMENT (CN1)**

|         |        | •                            |         |        |                                           |  |  |

|---------|--------|------------------------------|---------|--------|-------------------------------------------|--|--|

| Pin No. | Symbol | Function                     | Pin No. | Symbol | Function                                  |  |  |

| 1       | GND    | Connect to ground            | 15      | IF0    | Interfece energtion made calcut           |  |  |

| 2       | D7     |                              | 16      | IF1    | Interface operation mode select           |  |  |

| 3       | D6     |                              | 17      | VD1S   | Digital power source select               |  |  |

| 4       | D5     |                              | 18      | VSS    | Ground                                    |  |  |

| 5       | D4     | Data bus                     | 19      | VDD    | Supply voltage for logic                  |  |  |

| 6       | D3     | Data dus                     | 20      | CA1N   | DC/DC voltage converter                   |  |  |

| 7       | D2     |                              | 21      | CA1P   |                                           |  |  |

| 8       | D1     |                              | 22      | XV0    | Negative operating voltage of COM-drivers |  |  |

| 9       | D0     |                              | 23      | V0     | Positive operating voltage of COM-drivers |  |  |

| 10      | RSTB   | Reset                        | 24      | VG     | Power of SEG-drivers                      |  |  |

| 11      | RWR    | Read/write execution control | 25      | GND    | Connect to ground                         |  |  |

| 12      | ERD    | Read/write execution control | * 26    | A      | Supply voltage for backlight (+)          |  |  |

| 13      | A0     | Data/command display control | * 27    | K      | Supply voltage for backlight (-)          |  |  |

| 14      | CSB    | Chip select                  |         |        |                                           |  |  |

Note (\*) : Pin 26, 27 are used for backlight version

SPEC. REV.00 PAGE 2 OF 22

### **COUNTER DRAWING OF MODULE DIMENSION (No backlight version)**

#### **COUNTER DRAWING OF MODULE DIMENSION (LED site-lited backlight version)**

#### COUNTER DRAWING OF PIN OUT & BLOCK DIAGRAM

#### **ELECTRICAL CHARACTERISTICS**

| Conditions: | VSS=0V. | Ta=25°C |

|-------------|---------|---------|

|             |         |         |

| Item                          | Symbol | MIN.   | TYP. | MAX.   | Unit |

|-------------------------------|--------|--------|------|--------|------|

| Supply Voltage for Logic      | VDD    | 3.05   | 3.3  | 3.55   | V    |

| Supply Current for Logic      | IDD    | _      | 1.5  |        | mA   |

| Operating Voltage for LCD (*) | VLCD   | 15.7   | 16.5 | 17.3   | V    |

| 'High' Level Input Voltage    | VIH    | 0.7VDD | _    |        | V    |

| 'Low' Level Input Voltage     | VIL    | _      | _    | 0.3VDD | V    |

Note (\*): There is tolerance in optimum LCD driving voltage during production and it will be within the specified range.

#### Side/Array BL:

#### Constant voltage driving:

| Item                    | Symbol   | MIN. | TYP. | MAX. | Unit | Condition       |

|-------------------------|----------|------|------|------|------|-----------------|

| White backlight current | $I_{BL}$ | _    | 35   | 45   | mA   | $V_{BL} = 3.3V$ |

| Blue backlight current  | $I_{BL}$ | _    | 35   | 45   | mA   | $V_{BL} = 3.3V$ |

#### **ABSOLUTE MAXIMUM RATINGS**

Please make sure not to exceed the following maximum rating values under the worst application conditions

| Item                  | Symbol | Rating (for normal temperature) | Rating (for wide temperature) | Unit                 |

|-----------------------|--------|---------------------------------|-------------------------------|----------------------|

| Supply Voltage        | Vdd    | -0.3 to 4                       | -0.3 to 4                     | V                    |

| Input Voltage         | VT     | -0.3 to VDD +0.3                | -0.3 to VDD +0.3              | V                    |

| Operating Temperature | Topr   | 0 to 50                         | -20 to 70                     | $^{\circ}\mathbb{C}$ |

| Storage Temperature   | Tstg   | -10 to 60                       | -30 to 80                     | $^{\circ}\mathbb{C}$ |

#### REFERENCE CIRCUIT EXAMPLE

SPEC. REV.00 PAGE 6 OF 22

## INSTRUCTIONS TABLE

| INSTRUCTION            | Α0    | R/W    |      |      | C    | OMMAI | ND BY | TE   |      |      | DESCRIPTION                                                                  |

|------------------------|-------|--------|------|------|------|-------|-------|------|------|------|------------------------------------------------------------------------------|

| INSTRUCTION            | AU    | FC/ VV | D7   | D6   | D5   | D4    | D3    | D2   | D1   | D0   | DESCRIPTION                                                                  |

| 1.Extension Command    | 0     | 0      | 0    | 0    | 1    | 1     | EXT1  | 0    | 0    | EXT0 | Set extension instruction                                                    |

| Ext[1:0]=0,0 (Extensio | n Cor | nman   | d 1) |      |      |       |       |      |      |      |                                                                              |

| 2.Display ON/OFF       | 0     | 0      | 1    | 0    | 1    | 0     | 1     | 1    | 1    | DSP  | Set LCD display<br>DSP=0: Display off<br>DSP=1: Display on                   |

| 3.Inverse Display      | 0     | 0      | 1    | 0    | 1    | 0     | 0     | 1    | 1    | INV  | Set inverse display<br>INV=0: Normal display<br>INV=1: Inverse display       |

| 4.All Pixel ON/OFF     | 0     | 0      | 0    | 0    | 1    | 0     | 0     | 0    | 1    | AP   | Set all pixel on mode<br>AP=0: All pixel off mode<br>AP=1: All pixel on mode |

|                        | 0     | 0      | 1    | 1    | 0    | 0     | 1     | 0    | 1    | 0    | Set display control<br>CLD :Set CL dividing ratio                            |

| 5.Display Control      | 1     | 0      | 0    | 0    | 0    | 0     | 0     | CLD  | 0    | 0    | LF[4:0] : Set N-line inversion counter                                       |

|                        | 1     | 0      | DT7  | DT6  | DT5  | DT4   | DT3   | DT2  | DT1  | DT0  | DT[7:0] : Set the number of duty FI : Set the inversion type of              |

|                        | 1     | 0      | 0    | 0    | LF4  | FI    | LF3   | LF2  | LF1  | LF0  | frame at the end of common scan cycle                                        |

| 6.Power Save           | 0     | 0      | 1    | 0    | 0    | 1     | 0     | 1    | 0    | SLP  | Set power save mode<br>SLP=0: Sleep out mode<br>SLP=1: Sleep in mode         |

|                        | 0     | 0      | 0    | 1    | 1    | 1     | 0     | 1    | 0    | 1    | Set Page Address<br>Starting Page address:                                   |

| 7.Set Page Address     | 1     | 0      | YS7  | YS6  | YS5  | YS4   | YS3   | YS2  | YS1  | YS0  | 00h≦YS≦28h<br>Ending Page address:                                           |

|                        | 1     | 0      | YE7  | YE6  | YE5  | YE4   | YE3   | YE2  | YE1  | YE0  | YS≦YE≦28h                                                                    |

|                        | 0     | 0      | 0    | 0    | 0    | 1     | 0     | 1    | 0    | 1    | Set Column Address<br>Starting Column address:                               |

| 8.Set Column Address   | 1     | 0      | XS7  | XS6  | XS5  | XS4   | XS3   | XS2  | XS1  | XS0  | 00h≦XS≦FFh<br>Ending Column address:                                         |

|                        | 1     | 0      | XE7  | XE6  | XE5  | XE4   | XE3   | XE2  | XE1  | XE0  | XS≦XE≦FFh                                                                    |

| 9.Data Scan Direction  | 0     | 0      | 1    | 0    | 1    | 1     | 1     | 1    | 0    | 0    | Set normal/ inverse display of<br>address and address scan                   |

|                        | 1     | 0      | 0    | 0    | 0    | 0     | 0     | C/L  | MX   | MY   | direction                                                                    |

| 10.Write Data          | 0     | 0      | 0    | 1    | 0    | 1     | 1     | 1    | 0    | 0    | Write data to DDRAM                                                          |

|                        | 1     | 0      | D7   | D6   | D5   | D4    | D3    | D2   | D1   | D0   |                                                                              |

| 11.Read Data           | 0     | 0      | 0    | 1    | 0    | 1     | 1     | 1    | 0    | 1    | Read data from DDRAM                                                         |

|                        | 1     | 1      | D7   | D6   | D5   | D4    | D3    | D2   | D1   | D0   |                                                                              |

|                        | 0     | 0      | 1    | 0    | 1    | 0     | 1     | 0    | 0    | 0    | Set partial area<br>Starting partial display address:                        |

| 12.Partial In          | 1     | 0      | PTS7 | PTS6 | PTS5 | PTS4  | PTS3  | PTS2 | PTS1 | PTS0 | 00h≦PTS≦A1h<br>Ending partial display address:                               |

|                        | 1     | 0      | PTE7 | PTE6 | PTE5 | PTE4  | PTE3  | PTE2 | PTE1 | PTE0 | 00h≦PTE≦A1h                                                                  |

SPEC. REV.00 PAGE 7 OF 22

|                             |    |     |      |      | C    | OMMAI | ND BY | ΓΕ   |      |      |                                                                                                                          |

|-----------------------------|----|-----|------|------|------|-------|-------|------|------|------|--------------------------------------------------------------------------------------------------------------------------|

| INSTRUCTION                 | A0 | R/W | D7   | D6   | D5   | D4    | D3    | D2   | D1   | D0   | DESCRIPTION                                                                                                              |

| 13.Partial Out              | 0  | 0   | 1    | 0    | 1    | 0     | 1     | 0    | 0    | 1    | Exit the partial mode                                                                                                    |

| 14.Read/Modify/Write<br>In  | 0  | 0   | 1    | 1    | 1    | 0     | 0     | 0    | 0    | 0    | Enable read modify write                                                                                                 |

| 15.Read/Modify/Write<br>Out | 0  | 0   | 1    | 1    | 1    | 0     | 1     | 1    | 1    | 0    | Disable read modify write                                                                                                |

|                             | 0  | 0   | 1    | 0    | 1    | 0     | 1     | 0    | 1    | 0    |                                                                                                                          |

|                             | 1  | 0   | TL7  | TL6  | TL5  | TL4   | TL3   | TL2  | TL1  | TL0  |                                                                                                                          |

| 16.Scroll Area              | 1  | 0   | BL7  | BL6  | BL5  | BL4   | BL3   | BL2  | BL1  | BL0  | Set scroll area                                                                                                          |

|                             | 1  | 0   | NSL7 | NSL6 | NSL5 | NSL4  | NSL3  | NSL2 | NSL1 | NSL0 |                                                                                                                          |

|                             | 1  | 0   | 0    | 0    | 0    | 0     | 0     | 0    | SCM1 | SCM0 |                                                                                                                          |

| 17.Set Start Line           | 0  | 0   | 1    | 0    | 1    | 0     | 1     | 0    | 1    | 1    | Set scroll start address                                                                                                 |

| 17.Set Start Line           | 1  | 0   | SL7  | SL6  | SL5  | SL4   | SL3   | SL2  | SL1  | SL0  | 00h≦SL≦A1h                                                                                                               |

| 18.OSC ON                   | 0  | 0   | 1    | 1    | 0    | 1     | 0     | 0    | 0    | 1    | Turn on the internal oscillator                                                                                          |

| 19.OSC OFF                  | 0  | 0   | 1    | 1    | 0    | 1     | 0     | 0    | 1    | 0    | Turn off the internal oscillator                                                                                         |

| 20.Power Control            | 0  | 0   | 0    | 0    | 1    | 0     | 0     | 0    | 0    | 0    | Power circuit operation<br>VB=0: OFF, VB=1: ON<br>VF=0: OFF, VF=1: ON<br>VR=0: OFF, VR=1: ON                             |

| 20.Fower Control            | 1  | 0   | 0    | 0    | 0    | 0     | VB    | 0    | VF   | VR   |                                                                                                                          |

|                             | 0  | 0   | 1    | 0    | 0    | 0     | 0     | 0    | 0    | 1    |                                                                                                                          |

| 21.Set Vop                  | 1  | 0   | 0    | 0    | Vop5 | Vop4  | Vop3  | Vop2 | Vop1 | Vop0 | Set Vop                                                                                                                  |

|                             | 1  | 0   | 0    | 0    | 0    | 0     | 0     | Vop8 | Vop7 | Vop6 |                                                                                                                          |

| 22.Vop Control              | 0  | 0   | 1    | 1    | 0    | 1     | 0     | 1    | 1    | VOL  | Control Vop<br>VOL=0: Vop increase one step<br>VOL=1: Vop decrease one step                                              |

| 23.Read Register<br>Mode    | 0  | 0   | 0    | 1    | 1    | 1     | 1     | 1    | 0    | REG  | Set read register mode<br>REG=0: read the register value<br>of VPR[5:0]<br>REG=1: read the register value<br>of VPR[8:6] |

| 24.Nop                      | 0  | 0   | 0    | 0    | 1    | 0     | 0     | 1    | 0    | 1    | No operation                                                                                                             |

| 25.Read Status              | 0  | 1   | D7   | D6   | D5   | D4    | D3    | D2   | D1   | D0   | Read status byte                                                                                                         |

| 26.Data Format Select       | 0  | 0   | 0    | 0    | 0    | 0     | 1     | DO   | 0    | 0    | DO=0; LSB on bottom (Default)<br>DO=1; LSB on top                                                                        |

| 27 Dienlay Mode             | 0  | 0   | 1    | 1    | 1    | 1     | 0     | 0    | 0    | 0    | Set display mode                                                                                                         |

| 27. Display Mode            | 1  | 0   | 0    | 0    | 0    | 1     | 0     | 0    | 0    | DM   | DM=0 :Mono(Default)<br>DM=1 :4Gray Scale Mode                                                                            |

| 28.ICON Control             | 0  | 0   | 0    | 1    | 1    | 1     | 0     | 1    | 1    | ICON | Enable/Disable ICON<br>ICON=1 ; Enable<br>ICON=0 ; Disable                                                               |

SPEC. REV.00 PAGE 8 OF 22

|                         | COMMAND BYTE |     |    |      |           |      |      |      |      |      |                                                                            |

|-------------------------|--------------|-----|----|------|-----------|------|------|------|------|------|----------------------------------------------------------------------------|

| INSTRUCTION             | A0           | R/W | D7 | D6   | D5        | D4   | D3   | D2   | D1   | D0   | DESCRIPTION                                                                |

| Ext[1:0]=0,1 (Extension | n Cor        |     |    |      |           |      |      |      |      |      |                                                                            |

|                         | 0            | 0   | 0  | 0    | 1         | 1    | 0    | 0    | 1    | 0    |                                                                            |

| 29.Analog Circuit Set   | 1            | 0   | 0  | 0    | 0         | 0    | 0    | 0    | 0    | 0    | Set analog set<br>BE[1:0]: Booster efficiency set                          |

|                         | 1            | 0   | 0  | 0    | 0         | 0    | 0    | 0    | BE1  | BE0  | BS[2:0]: Set bias ratio                                                    |

|                         | 1            | 0   | 0  | 0    | 0         | 0    | 0    | BS2  | BS1  | BS0  |                                                                            |

| 30.Booster Level        | 0            | 0   | 0  | 1    | 0         | 1    | 0    | 0    | 0    | 1    | Set booster level                                                          |

| 00.000001 20701         | 1            | 0   | 1  | 1    | 1         | 1    | 1    | 0    | 1    | BST  | Cot Booter forei                                                           |

| 31. Driving Select      | 0            | 0   | 0  | 1    | 0         | 0    | 0    | 0    | 0    | DS   | Power type<br>DS=0: Internal (Default)<br>DS=1 :External                   |

| 32.High Power Mode      | 0            | 0   | 0  | 1    | 0         | 0    | 1    | 0    | 0    | HPM  | Set high power mode<br>HPM=0 ; Normal Mode<br>HPM =1 ; High Power Mode     |

|                         | 0            | 0   | 1  | 1    | 0         | 1    | 0    | 1    | 1    | 1    | Set auto-read instruction                                                  |

| 33.Auto Read Control    | 1            | 0   | 1  | 0    | 0         | XARD | 1    | 1    | 1    | 1    | -XARD=0: Enable auto read<br>XARD=1: Disable auto read                     |

| 34.OTP WR/RD            | 0            | 0   | 1  | 1    | 1         | 0    | 0    | 0    | 0    | 0    | OTP WR/RD control<br>WR/RD=0: Enable OTP read<br>WR/RD=1: Enable OTP write |

| Control                 | 1            | 0   | 0  | 0    | WR/<br>RD | 0    | 0    | 0    | 0    | 0    |                                                                            |

| 35.OTP Control Out      | 0            | 0   | 1  | 1    | 1         | 0    | 0    | 0    | 0    | 1    | OTP control out                                                            |

| 36.OTP Write            | 0            | 0   | 1  | 1    | 1         | 0    | 0    | 0    | 1    | 0    | OTP write                                                                  |

| 37.OTP Read             | 0            | 0   | 1  | 1    | 1         | 0    | 0    | 0    | 1    | 1    | OTP read                                                                   |

| 38.OTP Selection        | 0            | 0   | 1  | 1    | 1         | 0    | 0    | 1    | 0    | 0    | OTP selection control                                                      |

| Control                 | 1            | 0   | 1  | Ctrl | 0         | 1    | 1    | 0    | 0    | 1    | Ctrl=1: Disable OTP<br>Ctrl=0: Enable OTP                                  |

| 39.OTP Programming      | 0            | 0   | 1  | 1    | 1         | 0    | 0    | 1    | 0    | 1    | OTD                                                                        |

| Setting                 | 1            | 0   | 0  | 0    | 0         | 0    | 1    | 1    | 1    | 1    | OTP programming setting                                                    |

|                         | 0            | 0   | 1  | 1    | 1         | 1    | 0    | 0    | 0    | 0    |                                                                            |

|                         | 1            | 0   | 0  | 0    | 0         | FRA4 | FRA3 | FRA2 | FRA1 | FRA0 |                                                                            |

| 40.Frame Rate           | 1            | 0   | 0  | 0    | 0         | FRB4 | FRB3 | FRB2 | FRB1 | FRB0 | Frame rate setting in different temperature range                          |

|                         | 1            | 0   | 0  | 0    | 0         | FRC4 | FRC3 | FRC2 | FRC1 |      | tomporature range                                                          |

|                         | 1            | 0   | 0  | 0    | 0         | FRD4 | FRD3 | FRD2 | FRD1 | FRD0 |                                                                            |

|                         | 0            | 0   | 1  | 1    | 1         | 1    | 0    | 0    | 1    | 0    |                                                                            |

| 41.Temperature          | 1            | 0   | 0  | TA6  | TA5       | TA4  | TA3  | TA2  | TA1  | TA0  | Tomporature                                                                |

| Range                   | 1            | 0   | 0  | TB6  | TB5       | TB4  | TB3  | TB2  | TB1  | TB0  | Temperature range setting                                                  |

|                         | 1            | 0   | 0  | TC6  | TC5       | TC4  | TC3  | TC2  | TC1  | TC0  |                                                                            |

SPEC. REV.00 PAGE 9 OF 22

| INCTRUCTION                          |       | DAM  | İ    |      | C    | OMMAI | ND BY | ГΕ   |      |      | DESCRIPTION                                          |

|--------------------------------------|-------|------|------|------|------|-------|-------|------|------|------|------------------------------------------------------|

| INSTRUCTION                          | A0    | R/W  | D7   | D6   | D5   | D4    | D3    | D2   | D1   | D0   | DESCRIPTION                                          |

|                                      | 0     | 0    | 1    | 1    | 1    | 1     | 0     | 1    | 0    | 0    |                                                      |

|                                      | 1     | 0    | MT13 | MT12 | MT11 | MT10  | MT03  | MT02 | MT01 | MT00 |                                                      |

|                                      | 1     | 0    | MT33 | MT32 | MT31 | MT30  | MT23  | MT22 | MT21 | MT20 |                                                      |

| 42 Tomporatura                       | 1     | 0    | MT53 | MT52 | MT51 | MT50  | MT43  | MT42 | MT41 | MT40 |                                                      |

| 42.Temperature Gradient Compensation | 1     | 0    | MT73 | MT72 | MT71 | MT70  | MT63  | MT62 | MT61 | MT60 | Set temperature gradient<br>compensation coefficient |

|                                      | 1     | 0    | MT93 | MT92 | MT91 | MT90  | MT83  | MT82 | MT81 | MT80 | compensation coefficient                             |

|                                      | 1     | 0    | MTB3 | MTB2 | MTB1 | MTB0  | MTA3  | MTA2 | MTA1 | MTA0 |                                                      |

|                                      | 1     | 0    | MTD3 | MTD2 | MTD1 | MTD0  | MTC3  | MTC2 | MTC1 | MTC0 |                                                      |

|                                      | 1     | 0    | MTF3 | MTF2 | MTF1 | MTF0  | MTE3  | MTE2 | MTE1 | MTE0 |                                                      |

| Ext[1:0]=1,0(Extension               | 1 Com | mano | 3)   |      |      |       |       |      |      |      |                                                      |

| 43.Set ID                            | 0     | 0    | 1    | 1    | 0    | 1     | 0     | 1    | 0    | 1    | Set ID                                               |

| 45.56110                             | 1     | 0    | ID7  | ID6  | ID5  | ID4   | ID3   | ID2  | ID1  | ID0  | Set ID                                               |

| 44 Read ID                           | 0     | 0    | 0    | 1    | 1    | 1     | 1     | 1    | 1    | RID  | Read ID                                              |

| 44 Reau ID                           | 0     | 1    | D7   | D6   | D5   | D4    | D3    | D2   | D1   | D0   | RID=1 ; Enable<br>RID=0 ; Disable                    |

SPEC. REV.00 PAGE 10 OF 22

#### **DISPLAY DATA RAM**

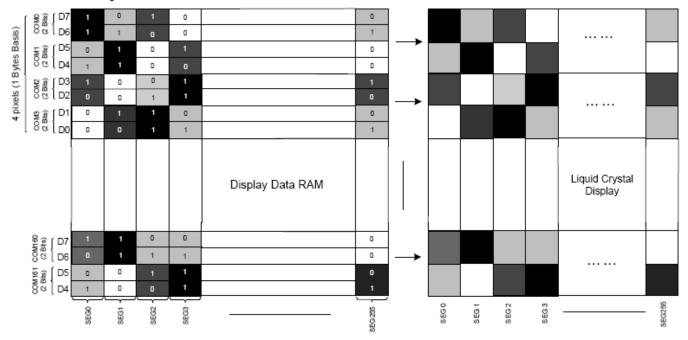

## 4-Level Gray Scale Mode

| 2 Bits | Data<br>0~3 | DDF | RAM    | LCD |  |  |  |

|--------|-------------|-----|--------|-----|--|--|--|

| D2N+1  | D2N         |     | U IIVI | LOD |  |  |  |

| 1      | 1           | 1   |        |     |  |  |  |

| 0      | 0           | 0   | 0 0    |     |  |  |  |

| 1      | 0           | 1   | 0      |     |  |  |  |

| 0      | 1           | 0   | 1      |     |  |  |  |

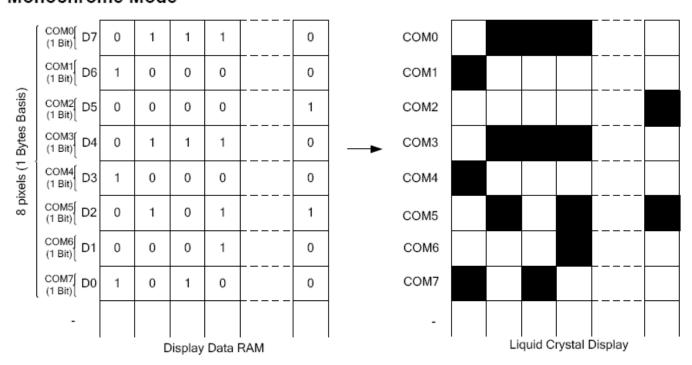

#### Monochrome Mode

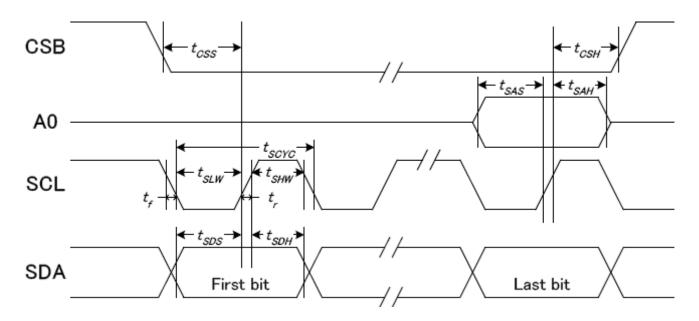

#### SERIAL INTERFACE TIMING DIAGRAM

## System Bus Timing for 4-Line SPI MCU Interface

VDD1 = 1.8~3.3V, Ta = 25°C

| Item                 | Signal | Symbol | Condition | Min. | Max. | Unit |

|----------------------|--------|--------|-----------|------|------|------|

| Serial clock period  |        | tSCYC  |           | 60   | _    |      |

| SCLK "H" pulse width | SCLK   | tSHW   |           | 30   | _    |      |

| SCLK "L" pulse width |        | tSLW   |           | 30   | _    |      |

| Address setup time   | A0     | tSAS   |           | 20   | _    |      |

| Address hold time    |        | tSAH   |           | 20   | _    | ne   |

| Data setup time      | 00.4   | tSDS   |           | 20   | _    | ns   |

| Data hold time       | SDA    | tSDH   |           | 20   | _    |      |

| CSB-SCLK time        |        | tCSS   |           | 20   | _    |      |

| CSB-SCLK time        | CSB    | tCSH   |           | 20   | _    |      |

| CS "H" pulse width   |        | tCHW   |           | 0    | -    |      |

#### Note:

- 1. The input signal rise and fall time (tr, tf) are specified at 15 ns or less.

- 2. All timing is specified using 20% and 80% of VDD1 as the standard.

SPEC. REV.00 PAGE 12 OF 22

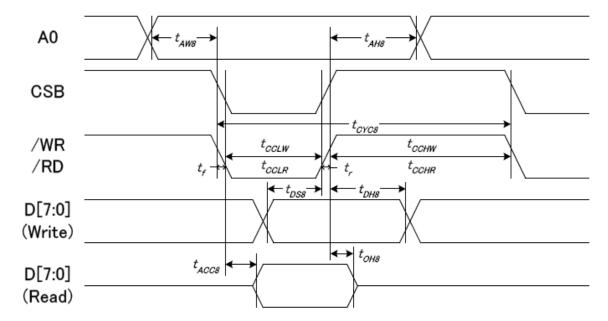

## System Bus Timing for 8080 MCU Interface

VDD1 = 1.8~3.3V, Ta = 25°C

| Item                      | Signal | Symbol | Condition  | Min. | Max. | Unit |

|---------------------------|--------|--------|------------|------|------|------|

| Address setup time        | - A0   | tAW8   |            | 20   | _    |      |

| Address hold time         | AU     | tAH8   |            | 0    | _    |      |

| System cycle time (WRITE) |        | tCYC8  |            | 160  | _    |      |

| /WR L pulse width (WRITE) | WR     | tCCLW  |            | 70   | _    |      |

| WR H pulse width (WRITE)  |        | tCCHW  |            | 70   | _    |      |

| System cycle time (READ)  |        | tCYC8  |            | 400  | _    | ne   |

| /RD L pulse width (READ)  | RD     | tCCLR  |            | 180  |      | ns   |

| /RD H pulse width (READ)  |        | tCCHR  |            | 180  |      |      |

| WRITE Data setup time     |        | tDS8   |            | 15   | _    |      |

| WRITE Data hold time      | D(7:01 | tDH8   |            | 15   | _    |      |

| READ access time          | D[7:0] | tACC8  | CL = 30 pF | _    | 100  |      |

| READ Output disable time  |        | tOH8   | CL = 30 pF | 10   | 110  |      |

#### Note:

- The input signal rise time and fall time (tr, tf) is specified at 15 ns or less. When the system cycle time is extremely fast, (tr + tf) ≤ (tCYC8 tCCLW tCCHW) for (tr + tf) ≤ (tCYC8 tCCLR tCCHR) are specified.

- 2. All timing is specified using 20% and 80% of VDD1 as the reference.

- tCCLW and tCCLR are specified as the overlap between CSB being "L" and WR and RD being at the "L" level.

SPEC. REV.00 PAGE 13 OF 22

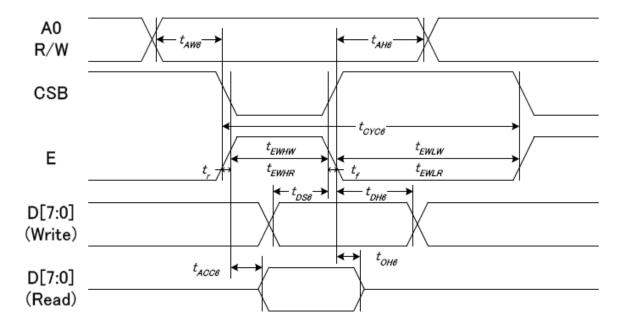

## System Bus Timing for 6800 MCU Interface

VDD1 = 1.8~3.3V, Ta = 25°C

| Item                          | Signal | Symbol | Condition  | Min. | Max. | Unit |

|-------------------------------|--------|--------|------------|------|------|------|

| Address setup time            | 40     | tAW6   |            | 20   | _    |      |

| Address hold time             | A0     | tAH6   |            | 0    | _    |      |

| System cycle time (WRITE)     |        | tCYC6  |            | 160  | _    |      |

| Enable L pulse width (WRITE)  | E      | tEWLW  |            | 70   | _    |      |

| Enable H pulse width (WRITE)  |        | tEWHW  |            | 70   | _    |      |

| System cycle time (READ)      |        | tCYC6  |            | 400  |      |      |

| Enable L pulse width (READ)   |        | tEWLR  |            | 180  | _    | ns   |

| Enable H pulse width (READ)   |        | tEWHR  |            | 180  |      |      |

| Write data setup time         |        | tDS6   |            | 15   | _    |      |

| Write data hold time          | D(7:0) | tDH6   |            | 15   | _    |      |

| Read data access time         | D[7:0] | tACC6  | CL = 30 pF | _    | 100  |      |

| Read data output disable time |        | tOH6   | CL = 30 pF | 10   | 110  |      |

#### Note:

- The input signal rise time and fall time (tr, tf) is specified at 15 ns or less. When the system cycle time is extremely fast, (tr + tf) ≤ (tCYC6 tEWLW tEWHW) for (tr + tf) ≤ (tCYC6 tEWLR tEWHR) are specified.

- 2. All timing is specified using 20% and 80% of VDD1 as the reference.

- 3. tEWLW and tEWLR are specified as the overlap between CSB being "L" and E.

SPEC. REV.00 PAGE 14 OF 22

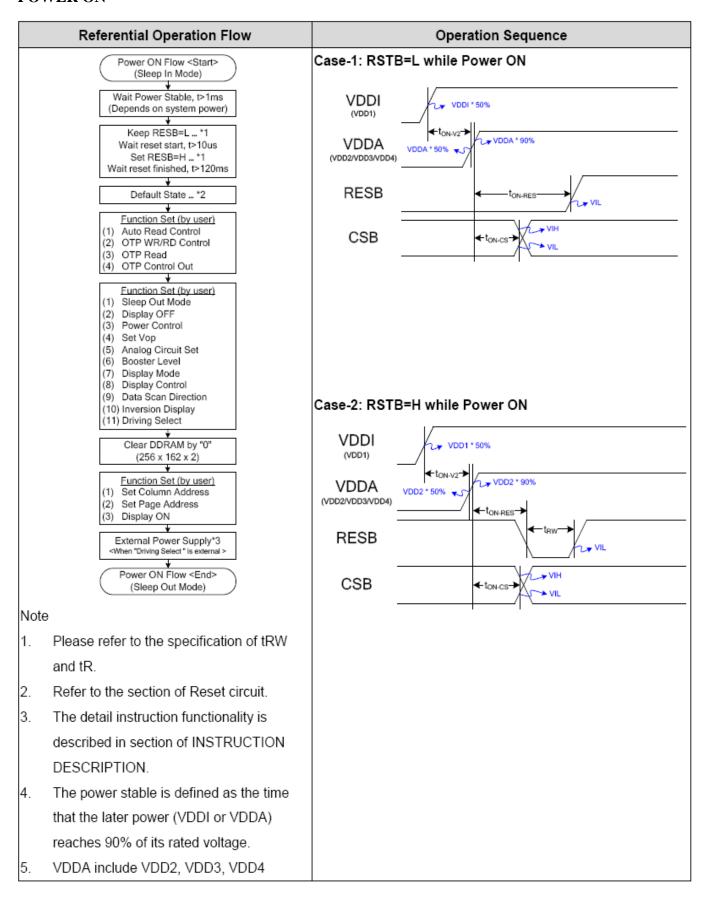

#### **POWER ON**

SPEC. REV.00 PAGE 15 OF 22

CG240160D

| Item                | Symbol              | Requirement             |     | Description                                                           |

|---------------------|---------------------|-------------------------|-----|-----------------------------------------------------------------------|

|                     |                     |                         | • \ | VDDI and VDDA can be applied in any order. IC                         |

|                     |                     |                         | ١   | will NOT be damaged when one of VDD1 and                              |

|                     |                     |                         | ١   | VDD2 is ON but another is OFF.                                        |

| VDD2 power ON delay | +                   | No Limitation           | • F | Power stable is defined as the time that the later                    |

| VDD2 power ON delay | t <sub>on-v2</sub>  | NO LITHIAGOT            | ŀ   | power (VDDI or VDDA) reaches 90% of its rated                         |

|                     |                     |                         | ١   | voltage.                                                              |

|                     |                     |                         | • F | Recommend Setting: -50ms $\leq$ $t_{ON-V2}$ $\leq$ No                 |

|                     |                     |                         | l   | Limitation.                                                           |

|                     |                     |                         | • [ | RESB=L can be input at any time after power is                        |

|                     | t <sub>on-res</sub> | Case-1                  | 9   | stable.                                                               |

| DESD input time     |                     | $t_{RW} \le t_{ON-RES}$ | • t | ${\rm t_{RW}}$ & ${\rm t_R}$ should match the timing specification of |

| RESB input time     |                     | Case-2                  | F   | RESB.                                                                 |

|                     |                     | No Limitation           | • F | RESB has priority over CSB.                                           |

|                     |                     |                         | • F | Recommend Setting: $0 \le t_{ON-RES} \le 50$ ms.                      |

| CSB input time      | +                   | No Limitation           | • ( | CSB can be input at any time after power is                           |

| CSB input time      | t <sub>on-cs</sub>  | NO LIMITATION           | 9   | stable.                                                               |

#### Note:

- 1. If the contents of internal registers are the same as default, the related commands can be ignored.

- If RESB is held high or unstable during power ON, a successful hardware reset by RSTB is required after VDDI and VDDA are both stable (as illustrated in Case-2). Otherwise, correct functionality can NOT be guaranteed.

SPEC. REV.00 PAGE 16 OF 22

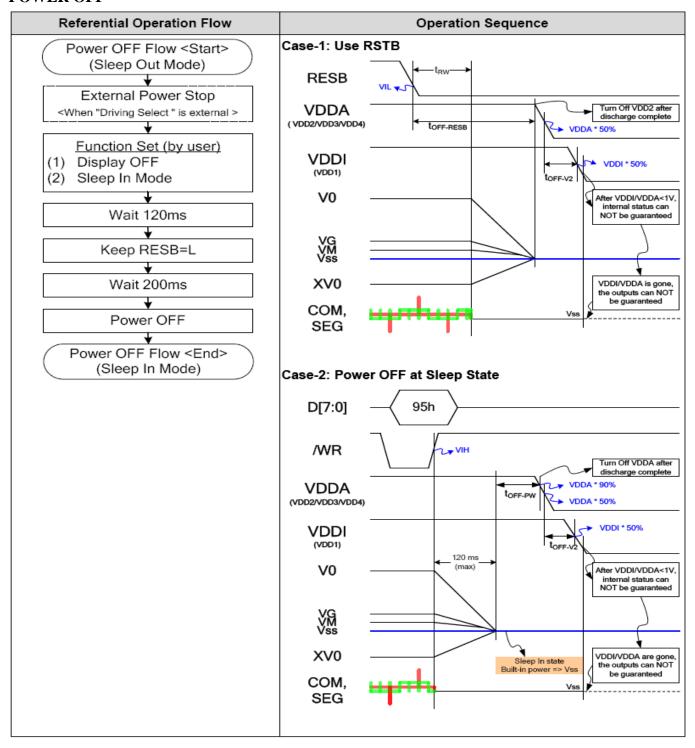

#### **POWER OFF**

| Item                |        | Symbol                | Requirement                  |                                          | Description                                         |  |

|---------------------|--------|-----------------------|------------------------------|------------------------------------------|-----------------------------------------------------|--|

| Power OFF           | Case-1 | t <sub>OFF-RESB</sub> | 200ms ≤t <sub>OFF-RESB</sub> | Power can be turned OFF after built-in ; |                                                     |  |

| Time                | Case-2 | t <sub>off-PW</sub>   | 0 ≤ t <sub>off-PW</sub>      | becomes VSS.                             |                                                     |  |

| •                   |        |                       |                              | •                                        | VDD1 and VDD2 can be powered down in any            |  |

|                     |        |                       |                              |                                          | order. IC will NOT be damaged when one of           |  |

| VDD2 power ON delay |        | t <sub>OFF-V2</sub>   | No Limitation                |                                          | VDD1 and VDD2 is ON but another is OFF.             |  |

|                     |        |                       |                              | •                                        | Recommend Setting: -50ms ≤ t <sub>OFF-V2</sub> ≤ No |  |

|                     |        |                       |                              |                                          | Limitation.                                         |  |

Note: In Case-2, RSTB can fall to VSS at the same time as VDDI.

SPEC. REV.00 PAGE 17 OF 22

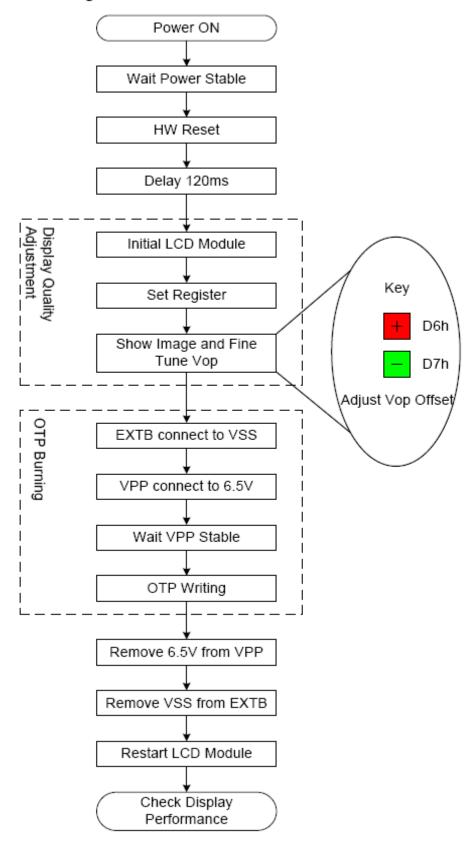

## Referential OTP Burning Flow

#### Note:

In this section "+" and "-" key button, please execute command D6h to increase one step at Vop and execute command D7h to decrease one step at Vop.

SPEC. REV.00 PAGE 18 OF 22

#### **ELECTRO-OPTICAL CHARACTERISTICS**

MEASURING CONDITION: POWER SUPPLY = Vop / 64 Hz TEMPERATURE =  $22 \pm 5$  °C

RELATIVE HUMIDITY =  $60 \pm 15 \%$

| ITEM           | SYMBOL | UNIT | TYP. STN |

|----------------|--------|------|----------|

| RESPONSE TIME  | Ton    | ms   | 320      |

|                | Toff   | ms   | 430      |

| CONTRAST RATIO | Cr     | -    | 8        |

|                | V3:00  | 0    | 40       |

| VIEWING ANGLE  | V6:00  | 0    | 55       |

| (Cr ≥ 2)       | V9:00  | 0    | 40       |

|                | V12:00 | 0    | 35       |

THE ELECTRO-OPTICAL CHARACTERISTICS ARE MEASURED VALUE BUT NOT GUARANTEED ONES.

### RELIABILITY OF LCD MODULE

|     |                              | TEST CONDITION                | TEST CONDITION                |           |

|-----|------------------------------|-------------------------------|-------------------------------|-----------|

| NO. | Item                         | FOR NORMAL TEMPERATURE        | FOR WIDE TEMPERATURE          | TIME      |

| 1   | High temperature operating   | 50°C                          | 70°C                          | 240 hours |

| 2   | Low temperature operating    | 0°C                           | -20°C                         | 240 hours |

| 3   | High temperature storage     | 60°C                          | 80°C                          | 240 hours |

| 4   | Low temperature storage      | -10°C                         | -30°C                         | 240 hours |

| 5   | Temperature-humidity storage | 40°C 90% R.H.                 | 60°C 90% R.H.                 | 96 hours  |

| 6   | Temperature cycling          | -10°C to 60°C                 | -30°C to 80°C                 | 5 avala   |

|     |                              | 30 Min Dwell                  | 30 Min Dwell                  | 5 cycle   |

| 7   | Vibration Test at LCM Level  | Freq 10-55 Hz                 | Freq 10-55 Hz                 |           |

|     |                              | Sweep rate: 10-55-10 at 1 min | Sweep rate: 10-55-10 at 1 min |           |

|     |                              | Sweep mode Linear             | Sweep mode Linear             | _         |

|     |                              | Displacement: 2 mm p-p        | Displacement: 2 mm p-p        |           |

|     |                              | 1 Hour each for X, Y, Z       | 1 Hour each for X, Y, Z       |           |

Inspection condition:

No. 1 ~ 6:

The samples should be placed in room temperature for 2 hours before inspection.

#### Acceptance criteria:

No non-conformance found in functional and cosmetic.

SPEC. REV.00 PAGE 19 OF 22

### **SAMPLING METHOD**

SAMPLING PLAN: MIL-STD 105E

CLASS OF AQL: LEVEL II/ SINGLE SAMPLING

MAJOR-0.65% MINOR – 1.5%

## **QUALITY STANDARD**

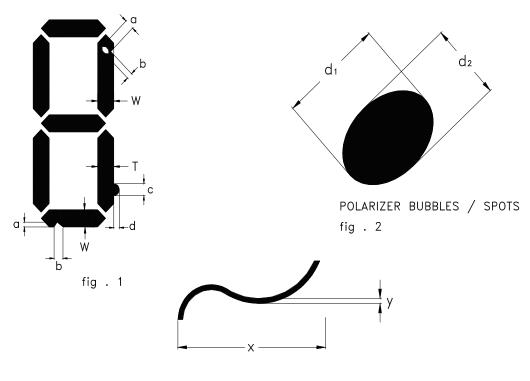

| DEFECT                 | CRITER                                                      | CRITERIA |       | FIGURE |

|------------------------|-------------------------------------------------------------|----------|-------|--------|

| SHORT CIRCUIT          | -                                                           |          | MAJOR | -      |

| MISSING SEGMENT        | -                                                           |          | MAJOR | -      |

| UNEVEN / POOR CONTRAST | -                                                           |          | MAJOR | -      |

| CROSS TALK             | -                                                           |          | MAJOR | -      |

| PIN HOLE               | $MAX(a,b) \leq 1/4 W$                                       |          | MINOR | 1      |

| EXCESS SEGMENT         | $MAX(c,d) \le 1/4 T$                                        |          | MINOR | 1      |

| BUBBLES                | d* ≥ 0.2                                                    | QTY=0    | MINOR | 2      |

| BLACKS SPOTS           | d ≤ 0.3                                                     | N.A.**   | MINOR | 2      |

|                        | 0.3 <d≤0.4< td=""><td>QTY≤1</td><td></td><td></td></d≤0.4<> | QTY≤1    |       |        |

|                        | 0.4 <d< td=""><td>QTY=0</td><td></td><td></td></d<>         | QTY=0    |       |        |

| LINE SCRATCHES         | x≥0.7 y≥0.05                                                | QTY=0    | MINOR | 3      |

| BLACK LINE             | x≥0.7 y≥0.05                                                | QTY=0    | MINOR | 3      |

\* $d = MAX(d_1,d_2)$

\*\* N. A . = NOT APPLICABLE

DEFECT TABLE : B

LINE SCRATCHES / BLACK LINE fig . 3

SPEC. REV.00

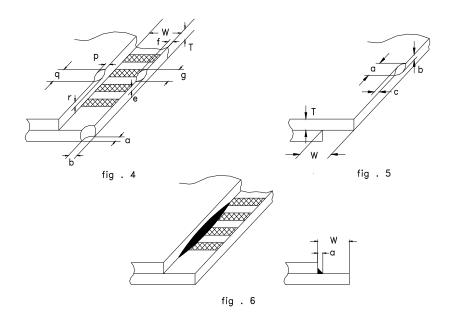

## $\ \, \textbf{QUALITY STANDARD} \ (\ \textbf{CONT}\ .)$

| DEFECT           |              | CRITERIA              | ТҮРЕ  | FIGURE |

|------------------|--------------|-----------------------|-------|--------|

|                  | CONTACT EDGE | e≤1/2T f≤1/3W g≤3.5   |       | 4      |

| CHIPS            | BOTTOM GLASS | p≤1.0 q≤3.5 r≤1/2T    | MINOR | 4      |

|                  | CORNER       | a≤1.5 b≤W             |       | 4      |

|                  | TOP GLASS    | a≤3.0 b≤1/3T c≤1/2W   |       | 5      |

| GLASS PROTRUSION |              | $a \le 1/4 \text{ W}$ | MINOR | 6      |

| RAINBOW          |              | -                     | MINOR | -      |

UNLESS STATE OTHERWISE , ALL UNIT ARE IN MILLIMETER .

DEFECT TABLE : B

SPEC. REV.00 PAGE 21 OF 22

#### HANDLING PRECAUTIONS

#### (1) CAUTION OF LCD HANDLING & CLEANING

Use soft cloth with solvent (recommended below) to clean the display surface and wipe lightly.

- Isopropyl alcohol, ethyl alcohol, trichlorotriflorothane

Do not wipe the display surface with dry or hard materials that will damage the polarizer surface. Do not use the following solvent;

-water, ketone, aromatics

#### (2) CAUTION AGAINST STATIC CHARGE

The LCD modules use CMOS LSI drivers, so customers are recommend that any unused input terminal would be connected to  $V_{DD}$  or  $V_{SS}$ , do not input any signals before power is turned on, and ground your body, work/assembly areas, assembly equipment to protect against static electricity.

Remove the protective film slowly and, if possible, under ESD control device like ion blower and humidity of working room should be kept over 50%RH to reduce risk of static charge.

#### (3) PACKAGING

Avoid intense shock and falls from a height and do not operate or store them exposed direct to sunshine or high temperature/humidity.

#### (4) CAUTION FOR OPERATION

It is an indispensable condition to drive LCD's within the specified voltage limit since the higher voltage than the limit causes the shorter LCD life. The use of direct current drive should be avoided because an electrochemical reaction due to direct current causes LCD's undesirable deterioration.

Response time will be extremely delayed at low temperature, and LCD's show dark color at high temperature. However those phenomena do not mean malfunction or out of order with LCD's.

Some font will be abnormally displayed when the display area is pushed hard during operation. But it resumes normal condition after turning off once.

#### (5) SOLDERING (for Pin type)

It is recommended to complete dip soldering at 270 °C or hand soldering at 280 °C within 3 seconds. The soldering position is at least 3mm apart from the pin head. Wave or reflow soldering are not recommended. Metal pins should not be soldered for more than 3 times and each soldering should be done after cool down of metal pins

#### (6) SAFETY

For crash damaged or unnecessary LCD's, it is recommended to wash off liquid crystal by either of solvents such as acetone and ethanol and should be burned up later.

When any liquid leaked out of a damaged glass cell comes in contact with your hands, wash it off with soap and water.

#### WARRANTY

CLOVER will replace or repair any of her LCD module in accordance with her LCD specification for a period of one year from date of shipment. The warranty liability of Clover is limited to repair and/or replacement. Clover will not be responsible for any subsequent or consequential event.

SPEC. REV.00 PAGE 22 OF 22